-

Notifications

You must be signed in to change notification settings - Fork 349

timer: Align SOF timer API with Zephyr #5393

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Conversation

|

@kkarask partial CI result, are we good to merge ? |

|

SOFCI TEST |

|

@lgirdwood We had a problem with one machine, the rerun is already going, after it it will be known if everything is ok. |

lyakh

left a comment

lyakh

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Sorry, maybe you could sketch approximately what next steps would be for the migration to the Zephyr timer API, maybe then it would be easier to understand where these changes are leading to?

|

@softwarecki lets also try and see how we can partition the xtos related APIs (as a code move) to src/arch/xtensa/xtos/. This way we can keep the generic code space clean. This could be a separate PR though, lets discuss it tomorrow. |

8efae32 to

8a967d0

Compare

@softwarecki can we not use some of these directly in this PR and create a wrapper for xtos (that calls the old APIs) ? This should simplify some of the other updates too (since they will be native APIs and be near xtos directory). |

8a6cdb1 to

76f4ac6

Compare

da4f10b to

5ed9d7c

Compare

|

Intel and MTK (and possible others) have 64bit timers alongside the xtensa CCOUNT 32bit timer. The Zephyr timer API is mostly 32bit today, but it uses the 64bit timer driver on Intel. I think there may be plans for full 64bit timer API on Zephyr @andyross ?. |

ok, ignore me ;) Things are moving fast, I think it fully 64 bit now, but I don't know if that also includes other APIs like scheduler that use time. |

i see the CCOUNT register is 32bit what i use |

|

I see. I think SOF / Zephyr uses 64 bit timers. if CCOUNT overflows then we increment the high 32 bits. See: sof/src/arch/xtensa/drivers/timer.c arch_timer_get_system |

|

Yes, but when i use So i think we should update xtensa_sys_timer.c this file, and add |

|

@lenghonglin you can use |

|

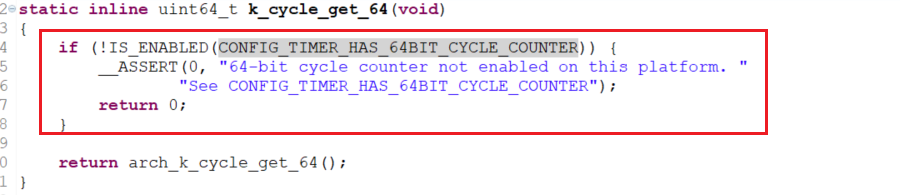

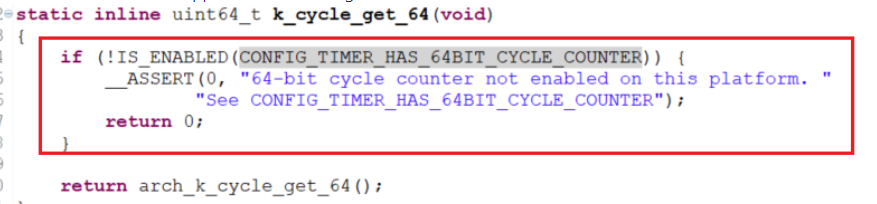

I understand your concern, and having a second look at it i might have my doubts too. Did you see any problems with the current implementation? For what I understand SOF generic layer uses k_cycle_get_64 and that's fine. But we need to understand how does that translates for IMX. Looking at zephyr: include/arch/xtensa/arch/arch.h we have: but I couldn't find the implementation of sys_clock_cycle_get_64. It must be there because the code compiles. I don't I understand what you are suggesting with adding sys_clock_cycle_get_32 |

Yes, it can be compiled, and I couldn't find the implementation of sys_clock_cycle_get_64 too, |

There is a question, see zephyrproject-rtos/zephyr#39935 this PR, though zephyr support 64 bit timer api , but the most important is the hardware should support 64bit timer register, or it should not be work. For |

Yes, I think should be support both |

Yes, but the common SOF code uses k_cycle_get_64 and it looks like this translates into nothing for IMX. Am i right, @lenghonglin |

|

We are looking into it, right now we don't know yet.

I believe, but still need to double check, that it is 32-bit. What kind of issues do you see/predict right now? |

I mean if the hardware not support |

|

Sorry, just catching up here. To answer the questions above: Zephyr's app-facing timeout API is selectable via CONFIG_TIMER_64BIT. If that is set to y (it's on by default), then all kernel timeouts are stored internally in a 64 bit count of ticks. The Zephyr driver interface remains mostly 32 bit internally, meaning that the longest delay between any two announced ticks must fit in a signed 32 bit integer. There hasn't been desire to augment this on any current platforms (rollover on the 38.4 MHz clock would be almost a full minute, for example), but if there's desire for that it would be easy to do. Finally the hardware cycle API, which is on top of the driver but parallel to the timeout system, is required to be only 32 bit. Recently we've seen drivers that want to expose the full counter via k_cycle_get_64(), which is what CONFIG_TIMER_HAS_64BIT_CYCLE_COUNTER is for. The cavs_timer driver for the HDA wall clock supports that just fine too. |

|

Yes, for support 32bit timer, I think it should better support |

|

@andyross @lenghonglin OK, Xtensa hifi4 only has 32bit timer register and for calls to Would it be possible to add support for k_cycle_get_64 by just keeping track of when ccount register overflows? e.g this implementation is used with SOF. SOF core code assumes that |

This way maybe cause confusion for developer. #if defined(__ZEPHYR__)

#ifdef TIMER_HAS_64BIT_CYCLE_COUNTER

#define sof_timer k_cycle_get_64

#else

#define sof_timer k_cycle_get_32

#endif

#endif |

@lenghonglin we should not be using any native SOF API call for RTOS functions (like timers) but use Zephyr conditional logic (at build time or runtime) like you have above to get the correct Zephyr native timer call. |

A regression bug was introduced by thesofprojectgh-5393 pull request. As a source of high precision CPU timestamp (aka "system" timer) this fix uses arch_timing_counter_get() for builds with Zephyr and timer_get_system(cpu_timer_get()) for SOF only builds. Note: arch_timing_counter_get() might not be implemented for your Zephyr platform. In this case k_cycle_get_64() is used instead. This will result in both "platform" and "cpu" timestamps to be equal. Signed-off-by: Serhiy Katsyuba <serhiy.katsyuba@intel.com>

A regression bug was introduced by gh-5393 pull request. As a source of high precision CPU timestamp (aka "system" timer) this fix uses arch_timing_counter_get() for builds with Zephyr and timer_get_system(cpu_timer_get()) for SOF only builds. Note: arch_timing_counter_get() might not be implemented for your Zephyr platform. In this case k_cycle_get_64() is used instead. This will result in both "platform" and "cpu" timestamps to be equal. Signed-off-by: Serhiy Katsyuba <serhiy.katsyuba@intel.com>

A regression bug was introduced by gh-5393 pull request. As a source of high precision CPU timestamp (aka "system" timer) this fix uses arch_timing_counter_get() for builds with Zephyr and timer_get_system(cpu_timer_get()) for SOF only builds. Note: arch_timing_counter_get() might not be implemented for your Zephyr platform. In this case k_cycle_get_64() is used instead. This will result in both "platform" and "cpu" timestamps to be equal. Signed-off-by: Serhiy Katsyuba <serhiy.katsyuba@intel.com> (cherry picked from commit 8e59c96)

The purpose of this PR is to prepare the SOF to use zephyr timer API.

Added functions platform_timer_ticks_to_ms and platform_timer_ticks_to_us which allows convert the time expressed in ticks to seconds.

Waiting for a certain time has been simplified by adding a functions wait_delay_ms and wait_delay_us. Previously now, its required a conversion between time to ticks using clock_ms_to_ticks.

New functions platform_timer_timeout_calc_ms and platform_timer_timeout_calc_us simplify the timeout calculation.