-

Notifications

You must be signed in to change notification settings - Fork 72

Open

Description

I tried to reproduce the results in this article.

I know that uarch-bench can use perf, but since I always get jevents errors, I made a simple implementation of this part of uarch-bench, and the code is here, which can be run directly from cont.sh .

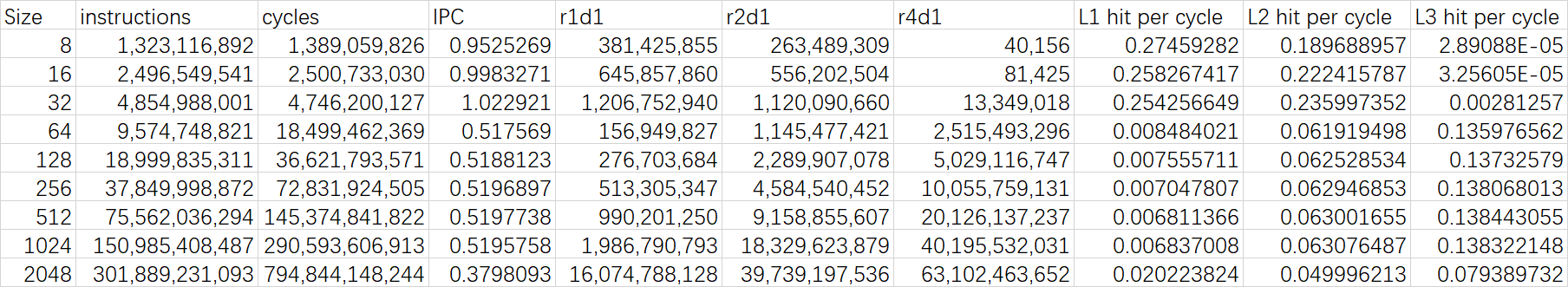

The experiments are done in my intel i7-10700. The data is shown below.

The three PMUs are explained as follows.

- r1d1: Retired load uops with L1 cache hits as data source

- r2d1: Retired load uops with L2 cache hits as data source

- r4d1: Retired load uops with L3 cache hits as data source

The first column size refers to the size of the Cache to be traversed, in Kib, with 500000 iterations.

The number of hits per cycle for the L1 and L2 cache is not quite the same as stated in the article, am I doing something wrong here?

Metadata

Metadata

Assignees

Labels

No labels