-

Notifications

You must be signed in to change notification settings - Fork 349

Backport bclk clock control to GLK branch #4249

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Backport bclk clock control to GLK branch #4249

Conversation

|

@slawblauciak @mwasko fyi. |

|

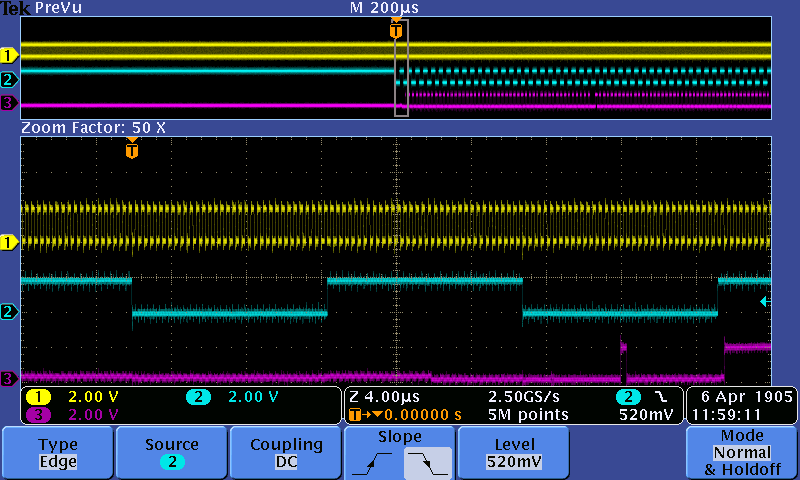

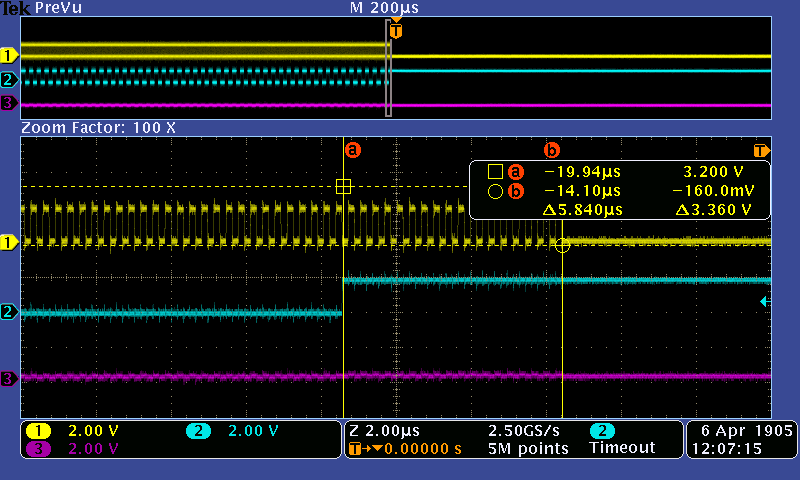

@plbossart yes, we will wait main branch finalized and see what's need to be ported to here. I've validated this PR on customer device and this is the result from oscilliscope:

As a side effect, this PR also fixes da7219 which PLL locks on fsync... |

That's why I'd like this change to become the default for all I2S codecs ;-) |

Yes, I took the topology patches with slight modification to PR #4219 |

557dabc to

4328afc

Compare

|

update to sync with #4288 |

|

Thanks @brentlu just to be clear. |

src/drivers/intel/cavs/ssp.c

Outdated

|

|

||

| spin_lock(&dai->lock); | ||

|

|

||

| trace_ssp("ssp_hw_free()"); |

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

this doesn't have to be under the lock

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

i think we need the lock to protect the ssp->state

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

@brentlu I meant the trace_ssp("ssp_hw_free()"); line

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

it's done. thanks for review

|

@plbossart both ODM and codec vendor could not find problem in this backport. Codec vendor still need to check the performance since bclk frequency is changed but basic function is ok. |

Good to know, thanks @brentlu |

The DAI_CONFIG IPC is currently used both for hw_params and hw_free. For some DAIs, there are hacky ways with e.g. invalid DMA channels to indicate a hw_free. Rather than adding a new IPC for hw_params and hw_free, let's add a flag that indicates if the DAI_CONFIG is really applied during a hw_params or hw_free stage. This is tagged as a ABI 3.19 change. Signed-off-by: Pierre-Louis Bossart <pierre-louis.bossart@linux.intel.com> (cherry picked from commit 0792297) Signed-off-by: Brent Lu <brent.lu@intel.com>

Add two clks_control bits. MCLK and/or BCLK will start during hw_params and stop during hw_free if the corresponding bit is set. This is tagged as a ABI 3.19 change. Signed-off-by: Bard Liao <yung-chuan.liao@linux.intel.com> (cherry picked from commit f46c144) Signed-off-by: Brent Lu <brent.lu@intel.com>

This will help identify support for SSP BCLK/MCLK changes. Signed-off-by: Pierre-Louis Bossart <pierre-louis.bossart@linux.intel.com> (cherry picked from commit 2c06163) Signed-off-by: Brent Lu <brent.lu@intel.com>

Some codecs need the SSP bit clock to start before data is provided, and conversely the bit clock to remain active until the hw_free stage. For backwards-compatibility with older kernels, the SOF_DAI_INTEL_SSP_CLKCTRL_MCLK_ES and SOF_DAI_INTEL_SSP_CLKCTRL_BCLK_ES bitfields are used to set an internal state in the ssp->clk_active field. This helps deals with the case where a topology sets these bits but the older kernel does not make use of the modified IPC. While we are at it, add clearer info traces for SSP configurations. Note that the FSYNC only starts when DMA transfers are enabled in the .trigger stage. This is by-design, the FSYNC will only start if the FIFO is not empty. During the prepare stages the DMA transfers are not enabled so the FIFOs are empty. To enable the FSYNC at an earlier stage, we would need a major surgery in the SOF architecture, or we would need to start zero-based DMA transfers. Co-developed-by: Pierre-Louis Bossart <pierre-louis.bossart@linux.intel.com> Signed-off-by: Pierre-Louis Bossart <pierre-louis.bossart@linux.intel.com> Signed-off-by: Bard Liao <yung-chuan.liao@linux.intel.com> (cherry picked from commit a0c1758) Signed-off-by: Brent Lu <brent.lu@intel.com>

The current code does not follow recommended programming sequences: TSRE and RSRE should be set before SSE and conversely cleared before SSE. Signed-off-by: Pierre-Louis Bossart <pierre-louis.bossart@linux.intel.com> (cherry picked from commit 99193ab) Signed-off-by: Brent Lu <brent.lu@intel.com>

Define the SSP_CC_MCLK/BCLK_ES bit to be used in SSP_CONFIG_DATA macro to enable mclk/bclk on hw_params and disable malk/bclk on hw_free. Signed-off-by: Brent Lu <brent.lu@intel.com> Signed-off-by: Bard Liao <yung-chuan.liao@linux.intel.com> (cherry picked from commit 61e4cd7) Signed-off-by: Brent Lu <brent.lu@intel.com>

Add support for cs42l42 running on GLK boards. There is a 10 ms BCLK delay in the master branch version to avoid the noise on TX path. However, this feature is not supported on GLK production branch yet so we remove it for now. Signed-off-by: Brent Lu <brent.lu@intel.com> (cherry picked from commit 45ce11022b40fe0fe8d998ee3f93a74b53fb7fd0) Signed-off-by: Brent Lu <brent.lu@intel.com>

Enable the bclk clock control for SSP2. Note that this impacts existing GLK-based chromebooks as well as newer hardware. Signed-off-by: Brent Lu <brent.lu@intel.com> Signed-off-by: Bard Liao <yung-chuan.liao@linux.intel.com> (cherry picked from commit 7199c68) Signed-off-by: Brent Lu <brent.lu@intel.com>

By changing bclk to 2.4MHz, we can use XTAL as clock source and reduce power consumption. Signed-off-by: Brent Lu <brent.lu@intel.com> (cherry picked from commit 5abd8a9) Signed-off-by: Brent Lu <brent.lu@intel.com>

Changing SSP2 configuration to use 24-bit sample bitwidth. Signed-off-by: Brent Lu <brent.lu@intel.com> (cherry picked from commit 44cc184dee0da1bcb9e1edd54d301b838b54c856) Signed-off-by: Brent Lu <brent.lu@intel.com>

|

based on the #4288 with topology changes to use 2.4MHz bclk and 24-bit sample width |

|

@mwasko @slawblauciak this one is for you. |

|

@brentlu I would recommend to create a separate branch for this change to avoid mess on release code that took place quite a long time ago. If you want to apply this fix on top of glk-012-stable-branch then I would like to propose to create glk-012-hot-fix-1 branch for that. |

|

Hi @mwasko, |

This PR is for ODM/codec vendor validation and review

The series of patches are originated from #4219 which is working on master branch. Since GLK branch is ancient, the implementation of bclk clock control is much simpler here but the idea is the same.